数字频率计

摘要

本文介绍了一种基于TTL系列芯片的简易数字频率计。数字频率计应用所学的数字电路知识进行设计。电路由放大整形电路、时基电路、逻辑控制电路、计数锁存电路及译码显示电路组成。能够较精准的测量幅值在0.2V~5V的正弦波、三角波、方波的频率。测量范围能够达到1Hz~9999Hz。

关键词:频率计,TTL芯片,数字电路

Abstract

In this paper,a design of simple digital cymometer based on the TTL serises chips was described.This design is based on the knowledge about the digital circuit we learned.It consists of amplifier and shaping circuit , time-base circuit, control circuit, latch circuit and decoding count show circuit.It can be used to accurately detect the frequency of sine wave, triangle wave and square wave accurately that the amplitude is between 0.2V and 5V. Detecting range can be achieved 1Hz ~ 9.99kHz..

Key words: cymometer, the TTL series chips,digital circuit

目录

摘要................................................................................................................................................. I

关键词............................................................................................................................................. I

Abstract.......................................................................................................................................... II

引言................................................................................................................................................. 1

1 总体方案设计.......................................................................................................................... 2

2 单元电路设计.......................................................................................................................... 3

2.1 放大整形电路............................................................................................................... 3

2.1.1 方案一................................................................................................................. 3

2.1.2 方案二................................................................................................................. 4

2.1.3 方案对比............................................................................................................. 4

2.2 时基电路....................................................................................................................... 5

2.2.1 方案一................................................................................................................. 5

2.2.2 方案二................................................................................................................. 5

2.2.3 方案对比............................................................................................................. 6

2.3 逻辑控制电路............................................................................................................... 6

2.4 计数器........................................................................................................................... 7

2.5 锁存器........................................................................................................................... 8

3 主要参数计算.......................................................................................................................... 9

3.1 时基电路参数............................................................................................................... 9

3.2 逻辑控制电路............................................................................................................... 9

4 总体电路设计........................................................................................................................ 10

5 仿真结果................................................................................................................................ 12

6 实物测试结果分析................................................................................................................ 14

7 体会与心得............................................................................................................................ 15

8 参考文献................................................................................................................................ 16

附录一 电路实物图..................................................................................................................... 17

附录二 元件清单......................................................................................................................... 18

引言

在电子技术中,频率是一个重要参量。应用计数法原理制成的数字式频率测量仪器具有精确度高,测频范围宽,便于实现测量过程自动化等一系列突出特点,所以数字式频率测量计(简称数字式频率计)已成为目前测量频率的主要仪器。

1 总体方案设计

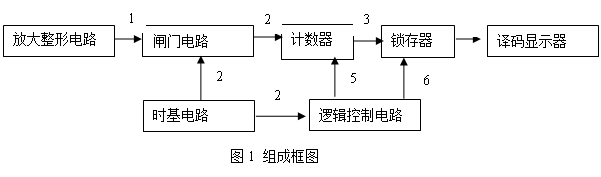

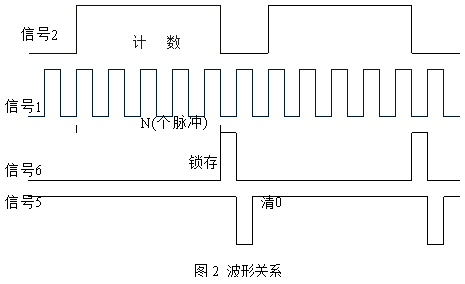

被测信号经过放大整形整形之后变成计数器所要求的脉冲信号1。标准时间基准信号2由时基电路提供其高电平持续时间为1s,计数器对1s时间中的脉冲计数,当1s信号结束时,时基电路产生信号2,闸门电路关闭,逻辑控制电路产生锁存信号6是显示器上的数字稳定,清零信号5是计数器从0开始计数。若在闸门时间1s内计数器计得的脉冲个数为N,则被测信号频率为N(Hz)。各信号的时序图如图二所示。

2 单元电路设计

2.1 放大整形电路

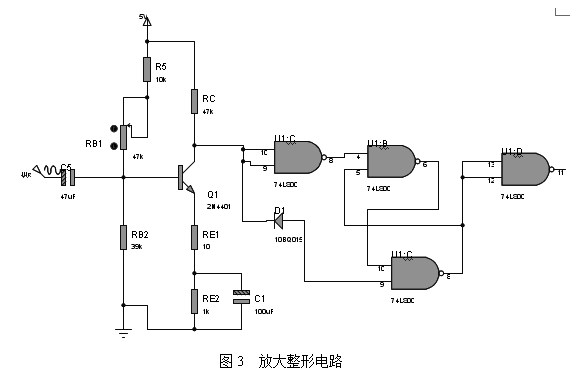

对信号的放大功能由三极管构成放大电路来实现,对信号整形的功能由施密特触发器来实现。施密特触发器电路是一种特殊的数字器件,一般的数字电路器件当输入起过一定的阈值,其输出一种状态,当输入小于这个阈值时,转变为另一个状态,而施密特触发器不是单一的阈值,而是两个阈值,一个是高电平的阈值,输入从低电平向高电平变化时,仅当大于这个阈值时才为高电平,而从高电平向低电平变化时即使小于这个阈值,其仍看成为高电平,输出状态不这;低电平阈值具有相同的特点。

2.1.1 方案一

放大整形电路由三极管与与非门组成。三极管构成的放大器将输入频率为fx 的周期信号如正弦波、三角波、等进行放大。将电源电压设为5V,当输入信号幅值比较大时,会出现线性失真,将放大后的波形幅度控制在5V以内。与非门构成施密特触发器对放大器的输出信号进行整形,使之成为矩形脉冲。电路图如图3所示。

2.1.2 方案二

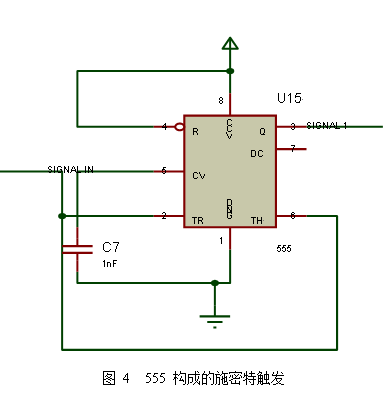

放大部分同方案一,整形部分是由555构成的施密特整形电路。电路图如图4所示。

2.1.3 方案对比

用与非门构成的施密特触发器因为阈值电压易受受温度、电源电压及干扰的影响,稳定性较差。而555定时器的比较器灵敏度高,输出驱动电路大,并且且555定时器构成的施密特触发器结构简单,而且抗干扰能力比用与非门构成的施密特触发器要强,因此选用方案二。

2.2 时基电路

时基电路

2.2.1 方案一

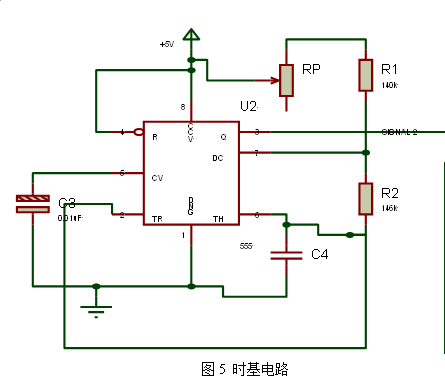

时基电路的作用是产生一个标准时间信号(高电平持续时间为1s)可用定时器555构成的多谐振荡器作为时基电路。多谐振荡器又称矩形波发生器,电路不具有稳定状态,但是具有两个暂稳态,当电路由一个暂稳态过渡到另一个暂稳态是,其“触发”信号是由电路内部电容充(放)电提供的,因此无需外部触发脉冲,电路工作就是在两个暂稳态之间来回转换。在此方案中时基信号2由引脚3输出。脉宽由电阻R1、R2及电容C4决定。电路图如图5所示。555定时器内部的比较器灵敏度高,而且采用差分电路形式,用555定时器组成的多谐振荡器的振荡频率受电源电压和温度变化的影响很小。

2.2.2 方案二

时基电路可用晶体振荡器和分频器构成。晶振频率取32768Hz,晶振产生脉冲经分频器14级二分频后输出2Hz脉冲(高、低电平各持续1s)。

2.2.3 方案对比

方案一中晶振分频产生标准时间精度要高于方案二中的555多谐振荡器产生的标准时间。但是555定时器电路元件较少,结构简单使用较方便。而且由于设计要求精度不是很高,所以采用方案二。

2.3 逻辑控制电路

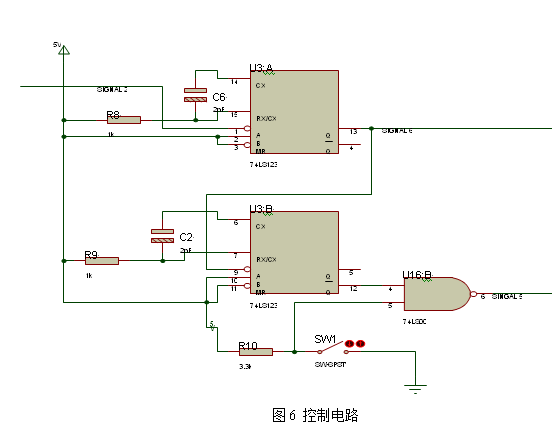

根据图2所示波形,在时基信号2结束时产生的下跳沿来产生锁存信号6,锁存信号6的下跳沿又用来产生清零信号5.脉冲信号6和5可由两个单稳态触发器74LS123产生,它们的脉冲宽度有电路的时间常数决定。电路如图6所示。

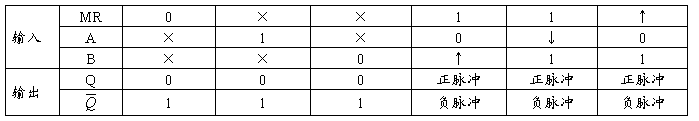

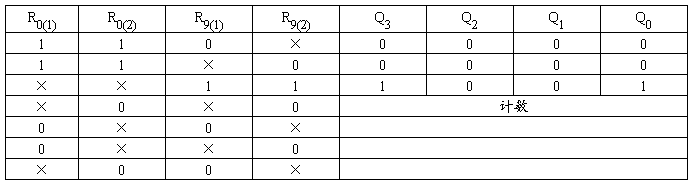

74LS123的功能表如下:

由74LS123的功能表可得当MR=B=1、触发脉冲从A端输入时,在触发脉冲的负跳变作用下,输出端Q可获得一个正脉冲, 端可获得一负脉冲。74LS123的12、13引脚的输出的波形关系正好满足图2所示波形5和6要求。手动复位开关S按下时,计数器清零。

端可获得一负脉冲。74LS123的12、13引脚的输出的波形关系正好满足图2所示波形5和6要求。手动复位开关S按下时,计数器清零。

2.4 计数器

该部分常用的二—五—十进制异步计数器74LS90。将Q0与 CPB相连,脉冲从CPA输入,构成8421BCD码十进制计数器。其功能表如表2所示

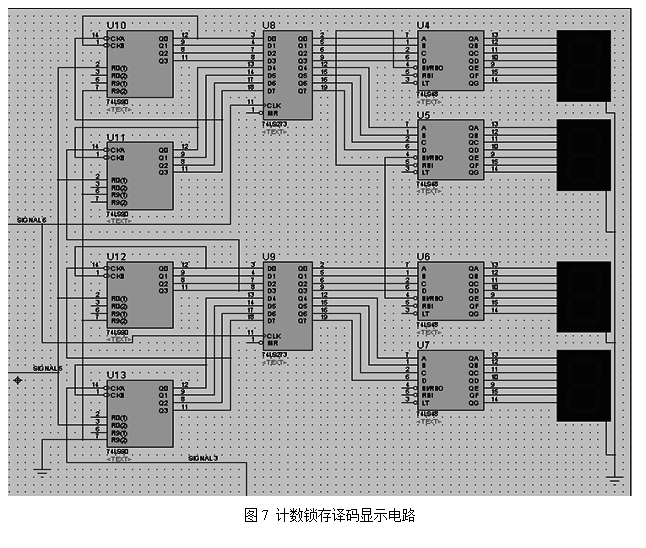

当R9(1)R9(2)=0,且R0(1)R0(2)=0时,计数器工作。计数器电路如图7所示,R9(1)=0,R0(1)=SIGNAL5(SINGAL5为逻辑控制电路产生的清零信号)。CPA输入要计数的脉冲。计数电路如图7所示。

2.5 锁存器

在1s的标准时间信号高电平结束时,锁存器将计数器此时所计得的数进行锁存,使显示器上能够稳定地显示此时计数器的值。如图2所示1s计数时间结束时,逻辑控制电路发出锁存信号6,将此时计数器的值送译码显示器。

可选用8D锁存器74LS273可以完成上述功能。当时钟脉冲CP的正跳变到来时,锁存器的输出等于输入,即Q=D。从而将计数器的输出值送到锁存器的输出端。正脉冲结束后,无论D为何值,输出端Q的状态人保持原来的状态不变。所以在计数期间内,计数器的输出不会送到译码器显示器,即显示器的示数不会变。计数锁存译码显示电路如图7。

3 主要参数计算

3.1 时基电路参数

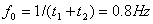

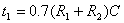

振荡器产生的时基信号高脉冲持续时间为 ,令低脉冲信号持续时间为

,令低脉冲信号持续时间为 ,那么振荡器的频率为

,那么振荡器的频率为

由公式:

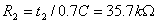

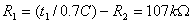

可计算出电阻 、

、 及电容C的值。若取电容

及电容C的值。若取电容 ,则

,则

取R239KΩ;

,取

,取

3.2 逻辑控制电路

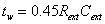

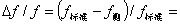

锁存信号6和清零信号5脉冲的总的宽度要小于时基信号负脉冲的宽度。令锁存信号和清零信号的脉冲宽度均为 ,则由公式

,则由公式

,

,

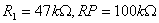

取电阻 ,则

,则

,取标称值

,取标称值

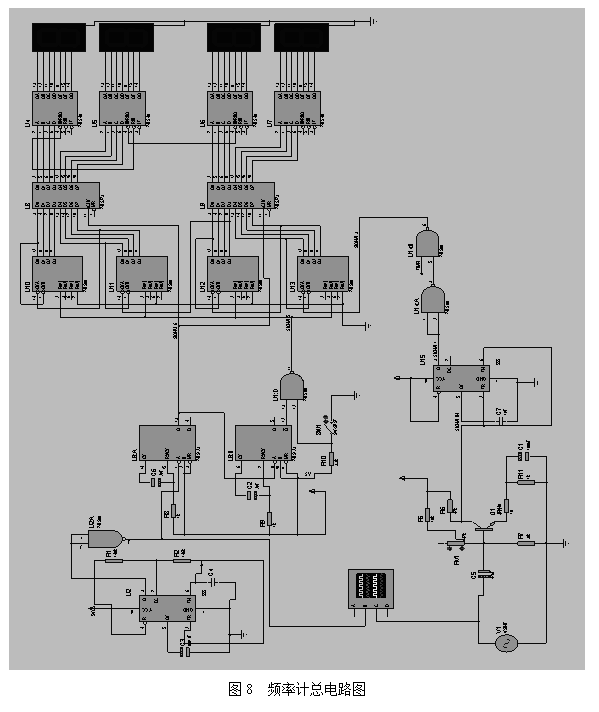

4 总体电路设计

被测信号经由晶体管3DG100组成的放大器放大后,送到由555构成的施密特触发器的输入端进行整形,使之成为计数器所要求的脉冲信号。由于放大电路的电源值为5V,所以输入信号比较大时,会出现线性失真,放大后的信号不会太大,超过5V。当时基脉冲处于高电平时,闸门电路打开,计数器对输入的脉冲进行计数。总电路图如图8所示。

时基脉冲高电平持续时间是1s。当1s计数结束时,闸门关闭,计数停止;74LS123的13引脚产生一个正脉冲,脉冲送到锁存器的时钟脉冲输入端,锁存器将计数器此时的结果锁存并显示。此时显示的数字就是被测信号的频率。74LS123的13引脚产生的正脉冲下调时,74LS123的12引脚产生一个负脉冲,对计数器进行清零。锁存和清零的全过程必须在时基信号处于低电平时完成,即在时基信号下一个高电平到来之前,74LS123的12引脚产生的负脉冲结束,恢复到高电平。如果在时基信号下一个高电平到来以后74LS123的12引脚产生的负脉冲才结束,那么计数器计的计算的将是少于1s的时间的脉冲个数,最后显示将小于实际值。

5 仿真结果

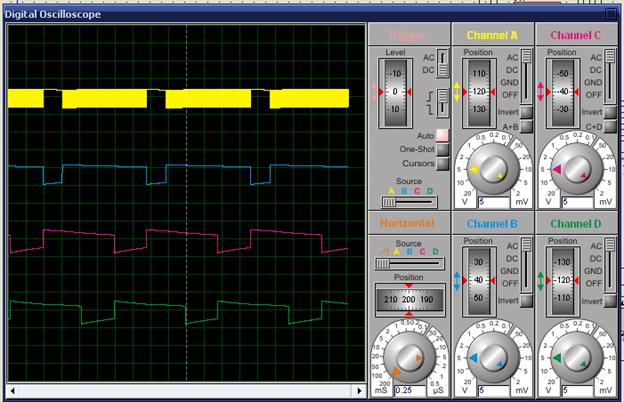

在软件Protus中画好电路图进行仿真。开始的仿真结果并不正确,显示的频率和设定的输入信号频率差距很大,例如输入信号频率设为100Hz,显示数值为46。经过观察各个功能模块的输出,通过分析发现问题出在控制电路产生的锁存信号和清零信号的脉冲宽度上,经过闸门电路后的信号、时基信号、锁存信号和清零信号的波形图如图9所示

波形从上到下依次为经过闸门电路后的信号、时基信号、锁存信号和清零信号。当时基信号的1s高电平结束时,锁存信号上跳,计数结果显示在数码管上,当锁存信号下跳,清零信号上跳,计数器清零端置“1”,直到清零信号脉冲结束,计数重新开始。从图9中可以看出,清零信号脉冲结束之前,时基信号早已处于高电平,所以计数不是从时基信号上跳时开始计数的,当1s的时基信号高脉冲还没结束时,清零信号又处于高电平状态。显示结果当然不正确。

检查逻辑控制部分电路,线路并没有连接错误,将元件参数改小一些后,结果还是没有错误。最后决定将时基信号低电平时间延长,设为2s。由于555定时器组成的多谐振荡器输出信号低电平持续时间是小于高电平持续时间的,所以在振荡器的输出加了一个反相器,以达到目的。

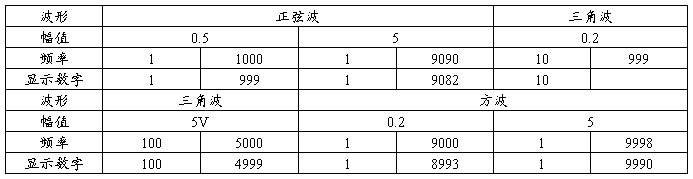

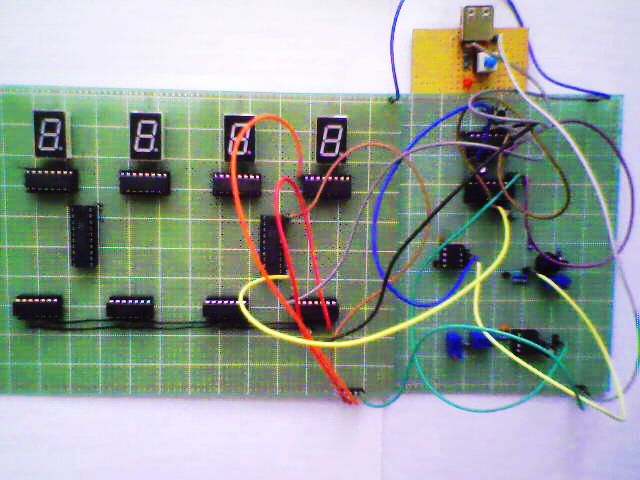

修改电路后仿真的结果如下:

当误差最大时,精确度为 0.008

0.008

因为74LS计数器是异步计数器,所以频率越高计数速度越慢。

6 实物测试结果分析

对所做实物进行测试时采用了先整体后局部的测试方法。

整体测试:

对电路进行整体测试时,数码管显示乱码,没有实现对频率进行测量的功能。故对电路进行分级测试,查看各部分功能是否实现。

局部测试:

由555定时器构成的时基电路实现设计所要求的矩形波发生器这一功能,高电平持续时间为1s,低电平持续时间为2s;由555定时器构成的施密特触发器实现了对波形进行整形的功能;基于74LS273的锁存电路部分能够实现对计数信号的锁存;基于74LS48的译码显示电路部分能够实现对锁存信号的译码显示功能。此外,由3DG130构成的放大电路,基于74LS90的计数电路和基于74LS00的清零电路都因为存在细节问题而暂时实现不了各自的功能,有待进一步检查修改。

7 体会与心得

在这次数字电子技术课程设计中,虽然应用的都是在书本上学过的知识,但是只有应用到实际中才算真正的学懂了这些知识。本次数字频率计的涉及到了三极管放大电路、555应用,单稳态触发器的延时应用,时序电路的计数、锁存,组合电路的译码显示等。涉及了数电所学的大部分内容。通过这次课程设计实践巩固了学过的知识并能够较好的利用。这对自己是一次很好的实践锻炼机会。

课程设计实践不单是将所学的知识应用于实际,在设计的过程中,只拥有理论知识是不够的。逻辑思维、电路设计的步骤和方法、考虑问题的思路和角度等也是很重要,需要我们着重注意锻炼的能力。在这次设计中还发现理论与实际常常常存在很大差距。譬如在这次设计中一开始仿真的结果和实际差距很大,通过对每个功能模块的认真分析,发现问题出在逻辑控制部分,在书本上学到的是74LS123输出的脉冲宽度为 ,但是在仿真过程中无论R、C的值如何改脉宽不变,为了使电路正常工作,必须灵活运用原理找出解决方法。

,但是在仿真过程中无论R、C的值如何改脉宽不变,为了使电路正常工作,必须灵活运用原理找出解决方法。

在实物调试的过程中,出现了很多问题,大部分都是电路连接问题,这说明自己的实际动手能力还不行。做实物毕竟和在电脑上仿真不一样,实物调试中总会出一些设计中必须考虑而在仿真中不会涉及的问题。所以做实物对于我们学习掌握电子电路知识是很有必要的。

最后我觉得我自己除了在数电知识方面的收获外,还学到了很多,比如在学习仿真软件Multisim、Proteus、Quartus II时,自己查资料进行摸索,逐渐发现这些软件大同小异,提高了软件的自学能力。并且在查阅资料时能够较有效率的得到自己想要的信息。而这些不是能从书本上得到的,是靠在实践中逐渐积累的。

8 参考文献

【1】 康华光. 《电子技术基础数字部分》 高等教育出版社

【2】 康华光. 《电子技术基础模拟部分》 高等教育出版社

【3】 谢子美. 《电子线路设计·实验·测试》第三版 华中科技大学出版社

【4】 瞿安连. 《应用电子技术》 科学出版社

【5】 梁宗善. 《新型集成电路的应用??电子技术基础课程设计》 华中科技大学出版社

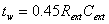

附录一 电路实物图

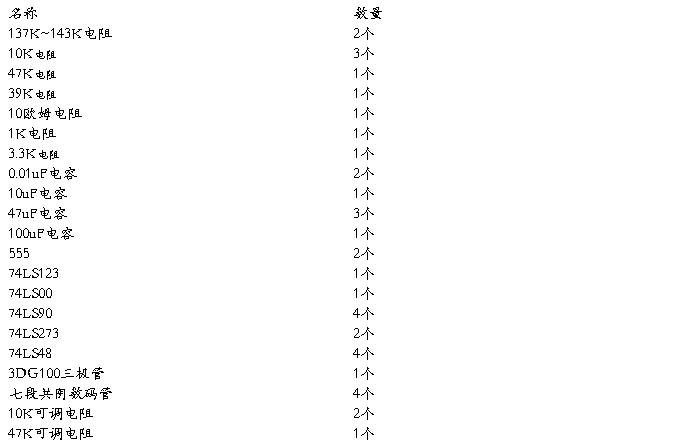

附录二 元件清单