实验一 门电路逻辑功能及测试

一、实验目的

1、熟悉门电路逻辑功能。

2、熟悉数字电路学习机及示波器使用方法。 二、实验仪器及材料 1、双踪示波器 2、器件

74LS00 二输入端四与非门 2片 74LS20 四输入端双与非门 1片 74LS86 二输入端四异或门 1片 74LS04 六反相器 1片 三、预习要求

1、复习门电路工作原理相应逻辑表达示。

2、熟悉所有集成电路的引线位置及各引线用途。 3、了解双踪示波器使用方法。 四、实验内容

实验前按学习机使用说明先检查学习机是否正常,然后选择实验用的集成电路,按自己设计的实验接线图接好连线,特别注意Vcc及地线不能接错。线接好后经实验指导教师检查无误方可通电。试验中改动接线须先断开电源,接好线后在通电实验。

1、测试门电路逻辑功能。

(1)选用双输入与非门74LS20一只,插入面包板,按图 连接电路,输入端接S1~S4(电平开关输入插口),输 出端接电平显示发光二极管(D1~D8任意一个)。

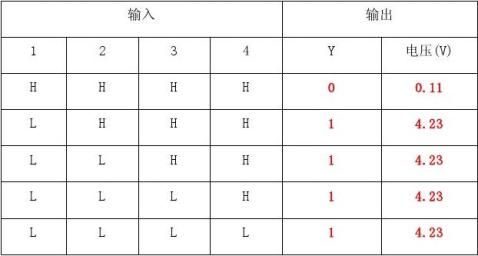

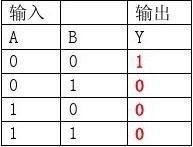

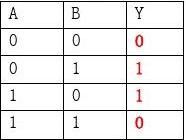

(2)将电平开关按表1.1置位,分别测出电压及逻辑状态。(表1.1)

2、异或门逻辑功能测试

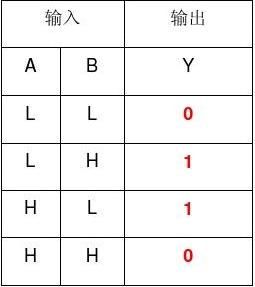

(1)选二输入四异或门电路74LS86,按图接线,输入端1?2?4?5接电平开关,输出端A?B?Y接电平显示发光二极管。 (2)将电平开关按表1.2置位,将结果填入表中。 表 1.2

(1)选用四二输入与非门74LS00一只,插入面包板,实验电路自拟。将输入输出逻辑关系分别填入表1.3?表1.4。

(2)写出上面两个电路的逻辑表达式。 表1.3 Y=A?B

表1.4 Y=A?B Z=AB 4、逻辑门传输延迟时间的测量

用六反相器(非门)按图1.5接线,输80KHz连续脉冲,用双踪示波器测输入,输出相位差,计算每个门的平均传输延迟时间的tpd值 : tpd=0.2μs/6=1/30μs 5、利用与非门控制输出。

选用四二输入与非门74LS00一只,插入面包板,输入接任一电平开关,用示波器观察

S对输出脉冲的控制作用:

一端接高有效的脉冲信号,另一端接控制信号。只有控制信号端为高电平时,脉冲信号才能通过。这就是与非门对脉冲的控制作用。

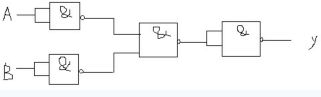

6.用与非门组成其他门电路并测试验证 (1)组成或非门。

用一片二输入端与非门组成或非门 Y = A+ B = A?

B

画出电路图,测试并填表1.5 中。 表1.5 图如下:

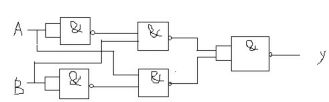

(2)组成异或门

① 将异或门表达式转化为与非门表达式。 A?B={[(AA)'B]'[A(BB)']}'

② 画出逻辑电路图。 ③ 测试并填表1.6。 表1.6

问题:

1、怎样判断门电路逻辑功能是否正常?

答:(1)按照门电路功能,根据输入和输出,列出真值表。(2)按真值表输入电平,查看它的输出是否符合真值表。(3)所有真值表输入状态时,它的输出都是符合真值表,则门电路功能正常;否则门电路功能不正常。

2、与非门一个输入接连续脉冲,其余端什么状态时允许脉冲通过?什么状态时禁止脉冲通过? 答:与非门接?电平则其他信号可以通过,接低电平则输出恒为0,与非门的真值表是“有0出1,全1出0”。所以一个输入接时钟,就是用时钟控制与非门,当时钟脉冲为高电平时,允许信号通过,为低电平时关闭与非门。

3、异或门又可称可控反向门,为什么? 答:因为当两输入端电平相同时,输出低电平0;当两输入端电平不同时,输出为1;这样就可以保证以上两种情况下,输入端信号可以同时取反相变化,而不改变逻辑门的状态。其输入端的 信号的相位是可以控制的,不影响逻辑门状态,故异或门又称位可控反相门。

第二篇:数电实验报告(1)

数字电子电路课程设计实验报告

江苏科技大学电子信息学院

一. 项目内容

用Verilog语言实现交通灯

二. 项目要求

1、满足如下时序要求:南北方向红灯亮,东西方向绿灯亮;南北方向绿灯亮,东西方向红灯亮;

2、 每一方向的红(绿)黄灯总共维持 30 秒;

3、 路口绿灯转红灯时,插入5秒黄灯闪烁时间,5秒后黄灯转入红灯同时另一方向路口转绿灯,一次工作循环结束,进入下一步另一方向的工作循环;

4、红绿黄灯均采用发光二极管;

5、夜间为黄灯闪耀。

三. 设计思路

1、对路口进行三十秒倒计时,设计一个倒数计时器,由于接入共阳极,故将输出分为高四位低四位分别接入两个数码管。

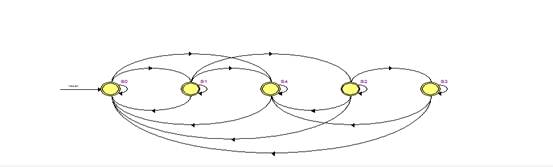

2、列写出状态表,画出状态图,明确状态之间的关系。

3、加入夜间模式的检测模块,将计数嵌套在倒数计时器中,每当计时器从30减至0时计数器加1,在计数大于一定值后自动跳入夜间模式。

4、为保证黄灯闪烁,在程序中加入分频器,将系统时钟分频,以便将黄灯和系统的时序脉冲区别开,让黄灯闪烁。

四. 设计程序

程序代码如下:

module Traffic(Time_H,Time_L,clk,Reset,out_z,out_y1,out_y2,n);

input clk,Reset;

output Time_H,Time_L;

output out_y1,out_y2;

output[3:0] out_z;

output[5:0] n;

reg[5:0] Current_State,Next_State,n;

reg[3:0] Time_H,Time_L,out_z;

reg[3:0] count_a = 4'b0000;

reg[1:0] count = 2'b00;

reg out_y1,out_y2,fout,clk1;

always@ ( posedge clk )// Demultiplication

begin

if(count_a <= 5)

count_a <= count_a + 1;

else

count_a <= 0;

end

always@ ( posedge clk )//10 Frequency

begin

if( count_a <= 5 )

clk1 <= 1;

else

clk1 <= 0;

end

always@(posedge clk1 or posedge Reset)//COUNTING

begin

if(Reset)

{Time_H,Time_L} <= 8'h30;

else if(n > 6'b110000)

n = 6'b000000;

else if({Time_H,Time_L} == 8'h00)//COUNTING FINISH

begin

{Time_H,Time_L} <= 8'h30;

n = n+6'b000001;

end

else if(Time_L == 4'h00)//Low -Order Position 0

begin

Time_H <= Time_H-1;

Time_L <= 4'h9;

end

else//Normal Circumstances

begin

Time_H <= Time_H;//High-Order Position

Time_L <= Time_L-1'h1;//Low -Order Position

end

end

always@(posedge clk)

begin

if(count == 2'b00)

begin

fout<= ~fout;

count <= 2'b11;

end

else

count <= count-2'b01;

end

always@(posedge clk1)//STAGE BEGIN

begin

if(Reset)

Current_State <= S0;

else

Current_State <= Next_State;//DEFINE OUTPUT

end

parameter//DEFINE PROCESSING

S0 = 6'b000001,

S1 = 6'b000010,

S2 = 6'b000100,

S3 = 6'b001000,

S4 = 6'b010000;

always@(Current_State or Time_L or Time_H)

begin

case(Current_State)

S0:begin//FIRST :SOUTH and NORTH RED,EAST and WEST GRE

if((Time_H == 0 && Time_L == 5)&& n < 6'b100100 )

Next_State <= S1;

else if( n >= 6'b100100 )

Next_State <= S4;

else

Next_State <= S0;

end

S1:begin//SECOND :SOUTH and NORTH RED,EAST and WEST YEL

if((Time_H == 0 && Time_L == 0)&& n < 6'b100100 )

Next_State <= S2;

else if( n >= 6'b100100 )

Next_State <= S4;

else

Next_State <= S1;

end

S2:begin//THIRD :SOUTH and NORTH GRE,EAST and WEST RED

if((Time_H == 0 && Time_L == 5)&& n < 6'b100100 )

Next_State <= S3;

else if( n >= 6'b100100 )

Next_State <= S4;

else

Next_State <= S2;

end

S3:begin//FORTH :SOUTH and NORTH YEL,EAST and WEST RED

if( n >= 6'b100100 )

Next_State <= S4;

else if((Time_H == 0 && Time_L == 0)&& n < 6'b100100)

Next_State <= S0;

else

Next_State <= S3;

end

S4:begin//SPECIAL:NIGHT MODEL

if( n >= 6'b110000 )

Next_State <= S0;//KEEP NIGHT MODEL

else

Next_State <= S4;//AFTER 5 O'CLOCK

end

default: Next_State <= S4;

endcase

end

always@(Current_State)//CODE NUMBER MEANING: SN-R,SN-G,EW-R,EW-G

begin

case(Current_State)

6'b000001:

begin

out_z <= 4'b1001;//SOU and NOR RED,EAST and WEST GRE

out_y1 <= 1'b0;

out_y2 <= 1'b0;

end

6'b000010:

begin

out_z <= 4'b1000;//SOU and NOR RED,EAST and WEST YEL

out_y1 <= 1'b0;

out_y2 <= fout;

end

6'b000100:

begin

out_z <= 4'b0110;//SOU and NOR GRE,EAST and WEST RED

out_y1 <= 1'b0;

out_y2 <= 1'b0;

end

6'b001000:

begin

out_z <= 4'b0010;//SOU and NOR YEL,EAST and WEST RED

out_y1 <= fout;

out_y2 <= 1'b0;

end

6'b010000:

begin

out_z <= 4'b0000;//NIGHT MODEL

out_y1 <= fout;

out_y2 <= fout;

end

default :

begin

out_z <= 4'b0000;

out_y1 <= 1'b0;

out_y2 <= 1'b0;

end

endcase

end

endmodule

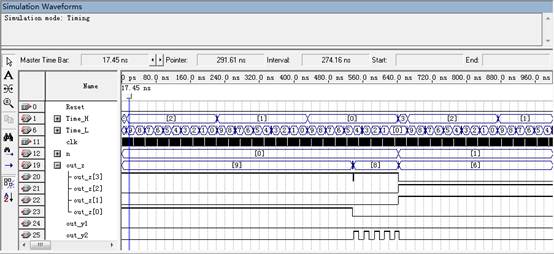

五. 状态图及仿真波形

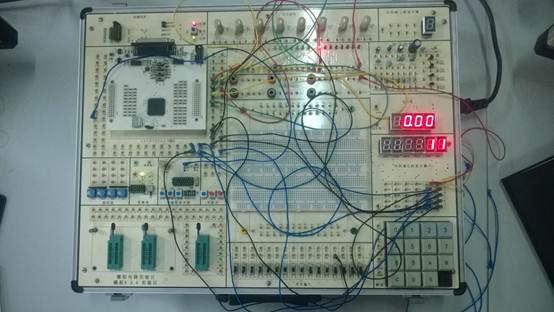

六. 实验线连接及下载调试

七. 实验总结

在这次课程设计中,小组成员认真研究状态机,分频器以及计时器的设计完成,在前期程序屡次达不到目标的时候进行思考,并对原有程序加以完善改良,后续加入夜间模式监测也得到了成功。通过本次设计,小组成员对数字电路有了更深的认识和学习,每个人的动手能力也得到了极大的提高。